GRAEME

DESIGNING WITH OPERATIONAL AMPLIFIERS Applications Alternatives

# DESIGNING WITH OPERATIONAL AMPLIFIERS

Wong and Ott · FUNCTION CIRCUITS

Graeme · DESIGNING WITH OPERATIONAL AMPLIFIERS

Graeme · APPLICATIONS OF OPERATIONAL AMPLIFIERS

Tobey, Graeme, and Huelsman · OPERATIONAL AMPLIFIERS

## DESIGNING WITH OPERATIONAL AMPLIFIERS

### **Applications Alternatives**

JERALD G. GRAEME

Manager, Monolithic Engineering Burr-Brown Research Corporation

### McGRAW-HILL BOOK COMPANY

New York St. Louis San Francisco Auckland Bogotá Düsseldorf Johannesburg London Madrid Mexico Montreal New Delhi Panama Paris São Paulo Singapore Sydney Tokyo Toronto

### Library of Congress Cataloging in Publication Data

Graeme, Jerald G

Designing with operational amplifiers.

(The BB electronics series)

Includes index.

1. Operational amplifiers. 2. Electronic circuits. 1. Title. 11. Series. TK7871.58.06G73 621.3815'35 76-44537 ISBN 0-07-023891-X

Copyright · 1977 by Burr-Brown Research Corporation. All rights reserved. Printed in the United States of America. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher.

678910 VBVB 876543

The information conveyed in this book has been carefully reviewed and is believed to be accurate and reliable; however, no responsibility is assumed for the operability of any circuit diagram or inaccuracies in calculations or statements. Further, nothing herein conveys to the purchaser a license under the patent rights of any individual or organization relating to the subject matter described herein.

The editors for this book were Tyler G. Hicks and Lester Strong, the designer was Naomi Auerbach, and the production supervisor was Frank P. Bellantoni. It was set in Caledonia by The Kingsport Press. Illustrated by Lola E. Graeme.

### **CONTENTS**

### Preface ix

| 1.1 DC Error Reduction 1 1.1.1 Continuous input offset voltage null 1.1.2 Input bias current compensation 4 1.2 Boosting Input Impedance 7 1.3 Power Boosters 10 1.3.1 Current boosters 10 1.3.2 Voltage boosters 12 1.4 Boosting Full-Power Response 15 1.5 Continuously Variable Gain Control 19 1.6 Switched Gain Control 23 1.6.1 Mechanical gain switching 24 1.6.2 Electronic gain switching 26  2. AMPLIFIERS |     | 1  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----|

| 1.3 Power Boosters 10 1.3.1 Current boosters 10 1.3.2 Voltage boosters 12 1.4 Boosting Full-Power Response 15 1.5 Continuously Variable Gain Control 19 1.6 Switched Gain Control 23 1.6.1 Mechanical gain switching 24 1.6.2 Electronic gain switching 26  2. AMPLIFIERS                                                                                                                                            |     |    |

| 1.3.1 Current boosters 10 1.3.2 Voltage boosters 12 1.4 Boosting Full-Power Response 15 1.5 Continuously Variable Gain Control 19 1.6 Switched Gain Control 23 1.6.1 Mechanical gain switching 24 1.6.2 Electronic gain switching 26  2. AMPLIFIERS                                                                                                                                                                  |     |    |

| 1.3.2 Voltage boosters 12  1.4 Boosting Full-Power Response 15 1.5 Continuously Variable Gain Control 19 1.6 Switched Gain Control 23 1.6.1 Mechanical gain switching 24 1.6.2 Electronic gain switching 26  2. AMPLIFIERS                                                                                                                                                                                           |     |    |

| 1.4 Boosting Full-Power Response 15 1.5 Continuously Variable Gain Control 19 1.6 Switched Gain Control 23 1.6.1 Mechanical gain switching 24 1.6.2 Electronic gain switching 26  2. AMPLIFIERS                                                                                                                                                                                                                      |     |    |

| 1.5 Continuously Variable Gain Control 19 1.6 Switched Gain Control 23 1.6.1 Mechanical gain switching 24 1.6.2 Electronic gain switching 26  2. AMPLIFIERS                                                                                                                                                                                                                                                          |     |    |

| 1.6 Switched Gain Control 23 1.6.1 Mechanical gain switching 24 1.6.2 Electronic gain switching 26  2. AMPLIFIERS                                                                                                                                                                                                                                                                                                    |     |    |

| 1.6.1 Mechanical gain switching 24 1.6.2 Electronic gain switching 26  2. AMPLIFIERS                                                                                                                                                                                                                                                                                                                                 |     |    |

| 2. AMPLIFIERS                                                                                                                                                                                                                                                                                                                                                                                                        | • • |    |

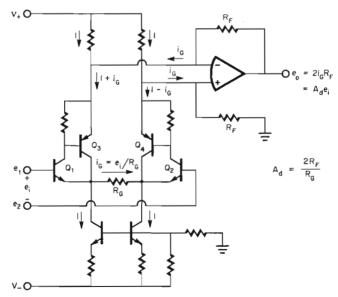

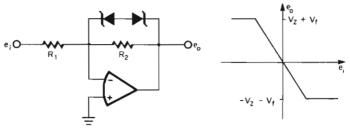

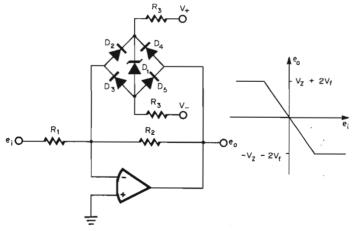

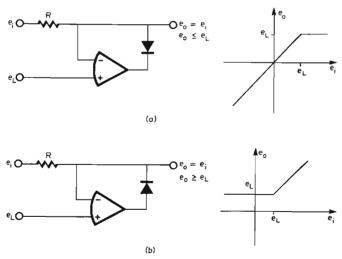

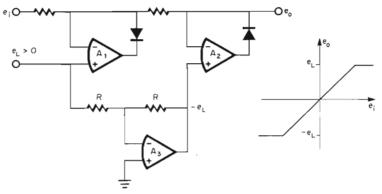

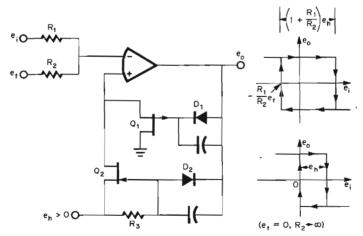

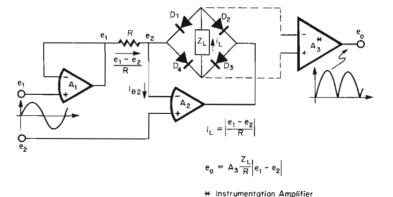

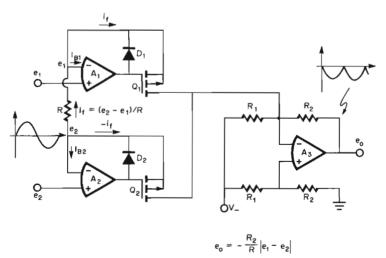

| 2. AMPLIFIERS  2.1 Instrumentation Amplifiers 31 2.2 DC Motor Control Amplifiers 35 2.3 Clamping Amplifiers 39 2.3.1 Zener diode-controlled clamping 30                                                                                                                                                                                                                                                              |     |    |

| <ul> <li>2.1 Instrumentation Amplifiers 31</li> <li>2.2 DC Motor Control Amplifiers 35</li> <li>2.3 Clamping Amplifiers 39</li> <li>2.3.1 Zener diode-controlled clamping 30</li> </ul>                                                                                                                                                                                                                              |     |    |

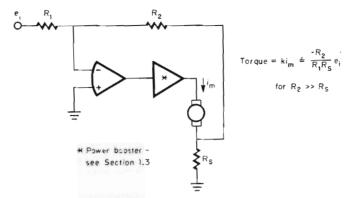

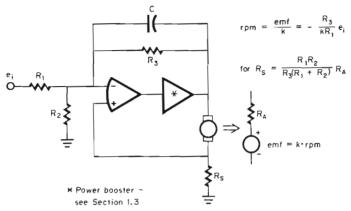

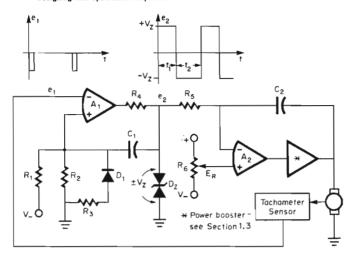

| 2.2 DC Motor Control Amplifiers 35 2.3 Clamping Amplifiers 39 2.3.1 Zener diode-controlled clamping 39                                                                                                                                                                                                                                                                                                               |     | 31 |

|                                                                                                                                                                                                                                                                                                                                                                                                                      | 39  |    |

### vi Contents

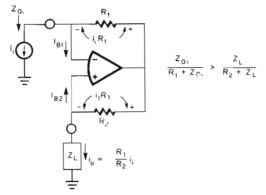

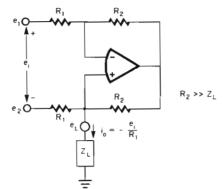

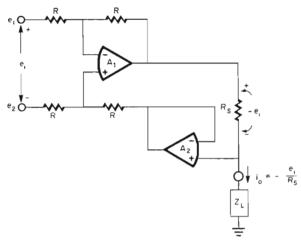

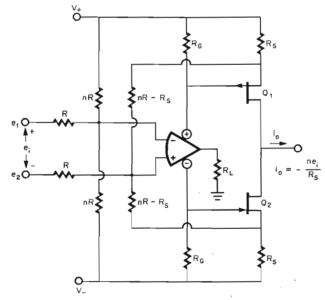

|    | 2.4        | Controlled Current Sources 47 2.4.1 Single-input current sources 47 2.4.2 Differential input current sources 50                                                                                                                                                |     |

|----|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3. | SIGN       | IAL ANALYZERS                                                                                                                                                                                                                                                  | 57  |

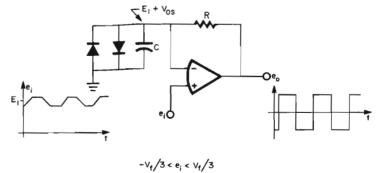

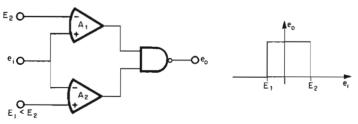

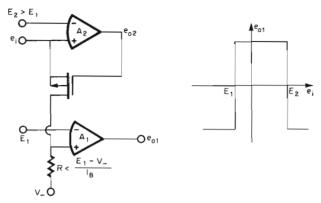

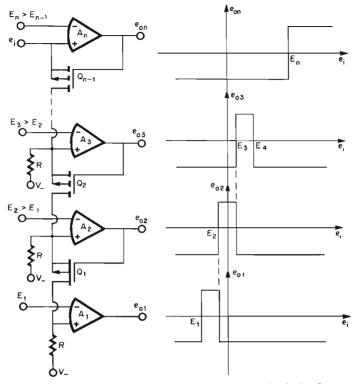

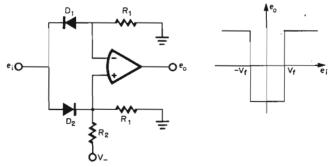

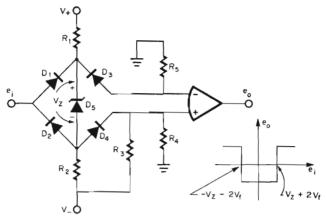

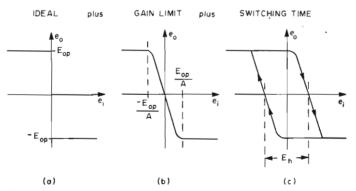

|    | 3.1        | Comparators 57 3.1.1 Specialized comparators 58 3.1.2 Window comparators 64 3.1.3 Reducing comparator hysteresis 69                                                                                                                                            |     |

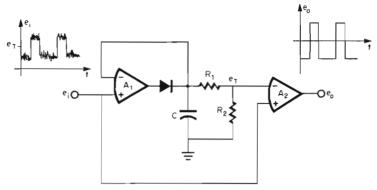

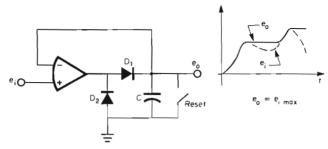

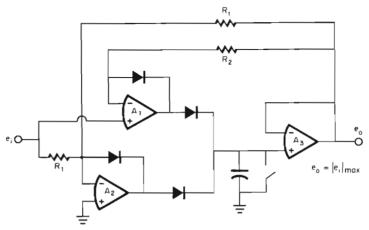

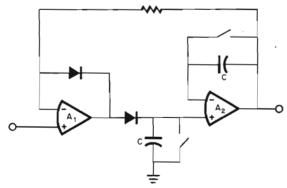

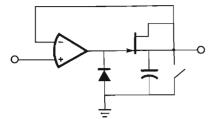

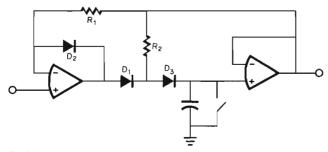

|    | 3.2        | Peak Detectors 76 3.2.1 Basic peak detectors 76 3.2.2 Specialized peak detectors 81 3.2.3 Improving peak detector accuracy 84                                                                                                                                  |     |

|    | 3.3        | 3.2.4 Improving peak detector speed 89 Voltage Discriminators 93                                                                                                                                                                                               |     |

| 4. | SIGN       | NAL CONDITIONERS                                                                                                                                                                                                                                               | 99  |

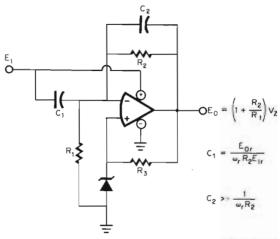

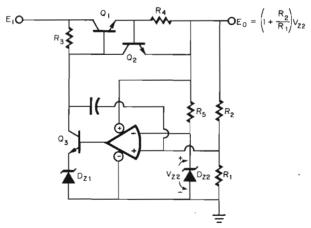

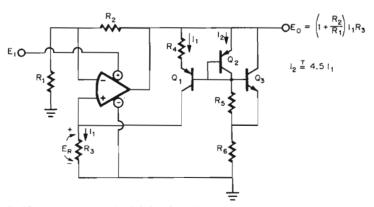

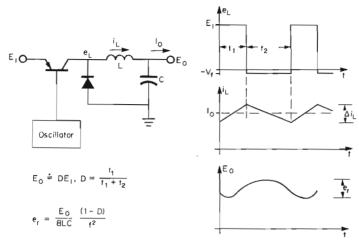

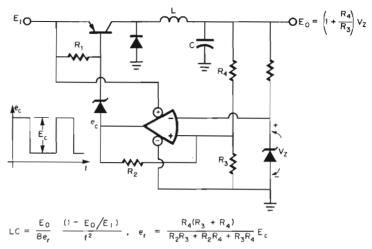

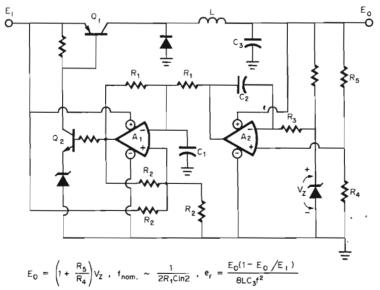

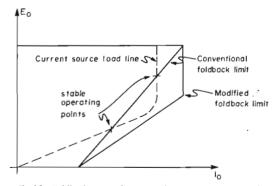

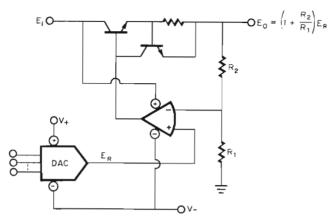

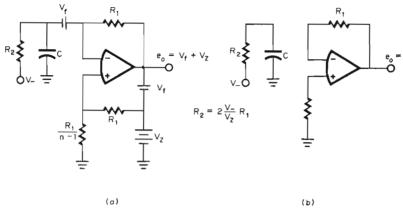

|    | 4.1        | Voltage Regulators 99 4.1.1 General-purpose circuits 100 4.1.2 Switching regulators 105 4.1.3 Specialized voltage regulators 111 4.1.4 Extending regulator utility 113                                                                                         |     |

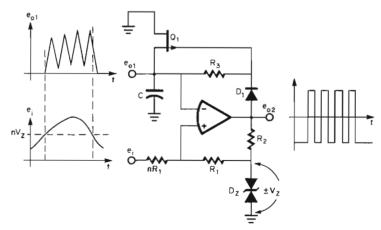

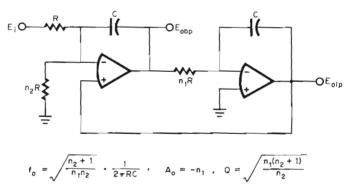

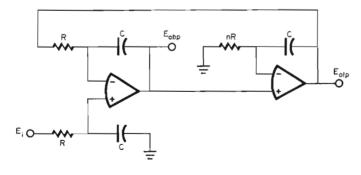

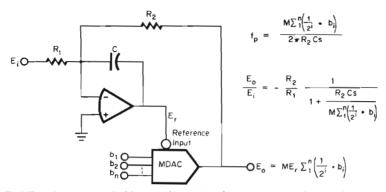

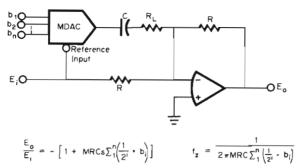

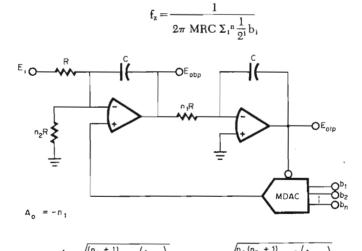

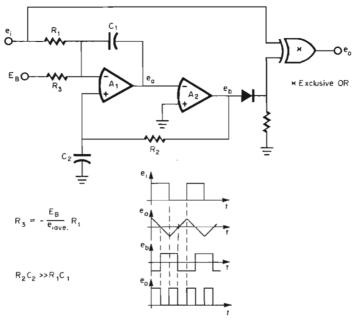

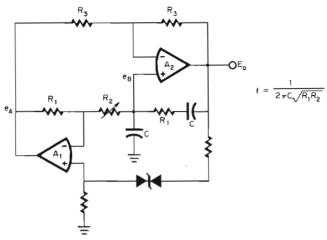

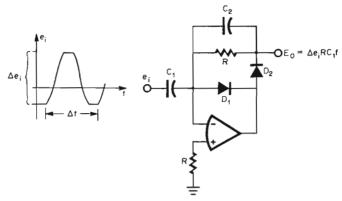

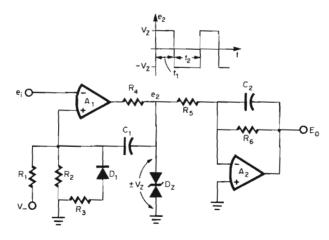

|    | 4.2        | Active Filters 115 4.2.1 Simplified state-variable configurations 116 4.2.2 Digitally controlled active filters 118 Frequency Multipliers 121                                                                                                                  |     |

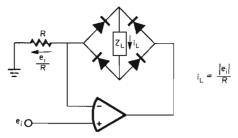

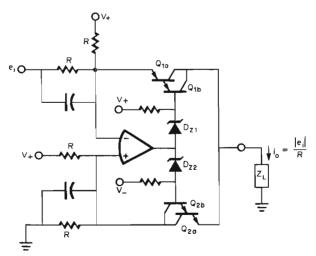

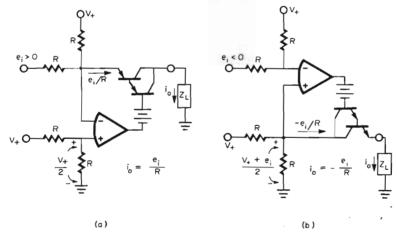

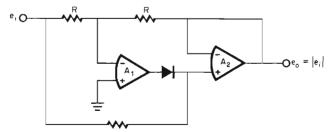

| 5. | ABS        | OLUTE-VALUE CIRCUITS                                                                                                                                                                                                                                           | 126 |

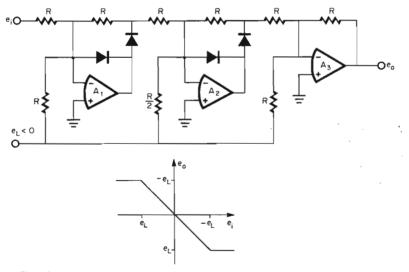

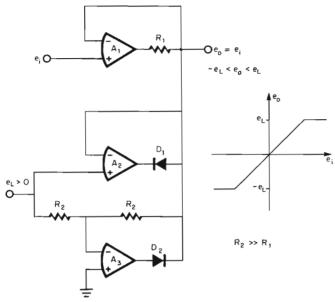

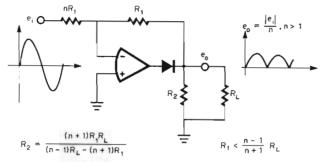

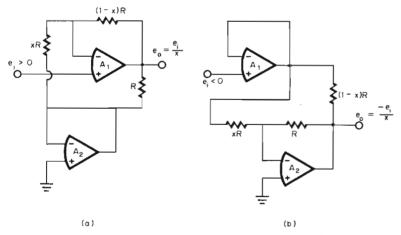

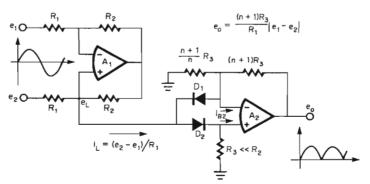

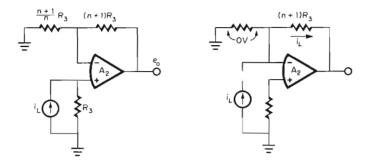

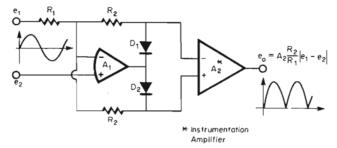

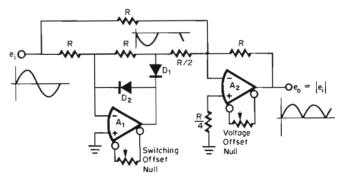

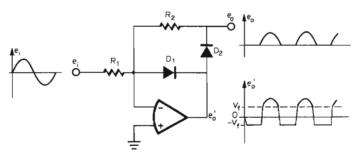

|    | 5.3        | Single Amplifier Configurations 126 Precision Absolute-Value Circuits 130 Differential Input Absolute-Value Circuits 136 Absolute-Value Circuit Response Improvements 143 5.4.1 Removing dc errors 144 5.4.2 Extending absolute-value conversion bandwidth 145 |     |

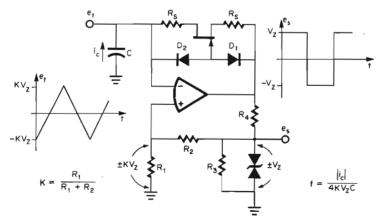

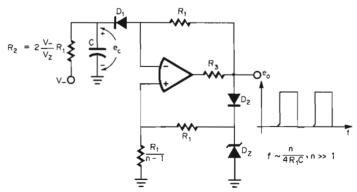

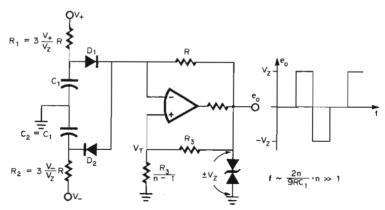

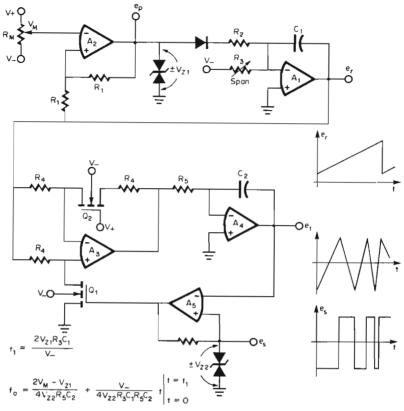

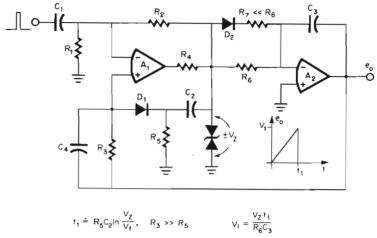

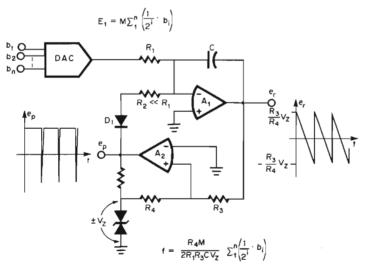

| 6. | SIG        | NAL GENERATORS                                                                                                                                                                                                                                                 | 149 |

|    | 6.4        | Ramp and Pulse Generators 161                                                                                                                                                                                                                                  |     |

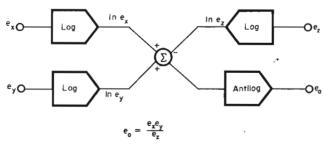

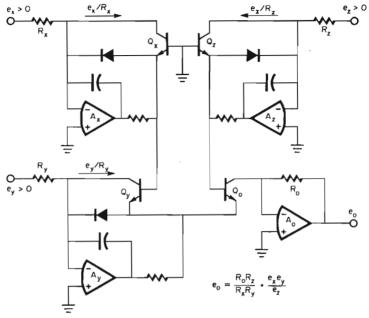

| 7. | COM        | IPUTING CIRCUITS                                                                                                                                                                                                                                               | 174 |

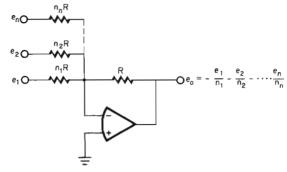

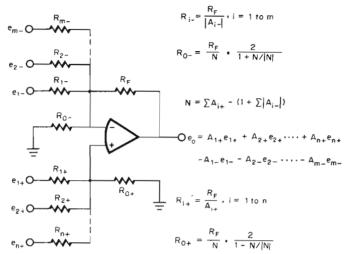

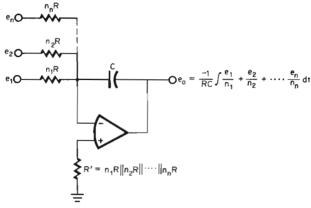

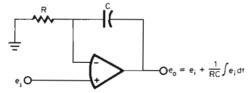

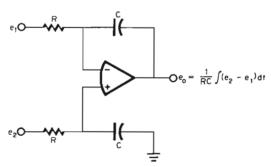

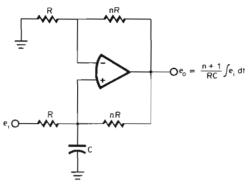

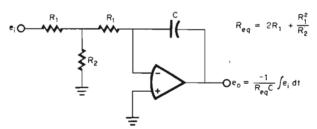

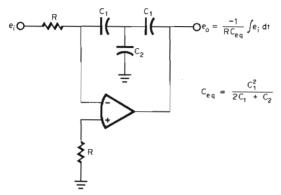

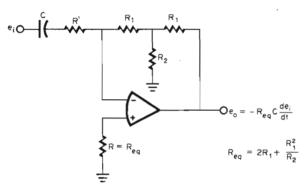

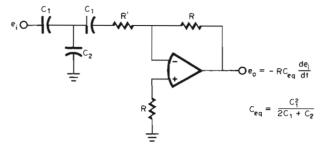

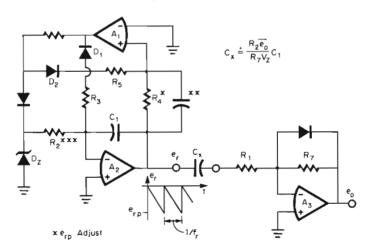

|    | 7.1<br>7.2 | Adders and Subtractors 174 Integrators 177 7.2.1 Summing and noninverting integrators 177 7.2.2 Extending integrator time constants 181                                                                                                                        |     |

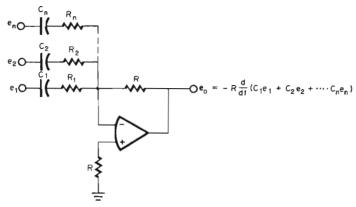

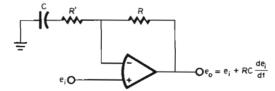

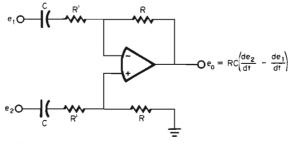

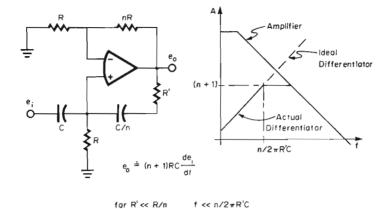

|    | 7.3<br>7.4<br>7.5 | 7.3.1 Summing and noninverting differentiators 182 7.3.2 Extending differentiator time constants 185     |     |  |  |

|----|-------------------|----------------------------------------------------------------------------------------------------------|-----|--|--|

|    | 7.6               | Specialized Functions 196                                                                                |     |  |  |

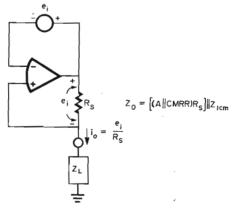

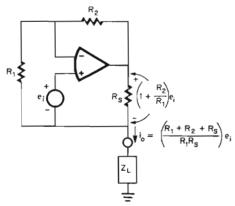

| 8. | DATA              | TRANSMISSION CIRCUITS                                                                                    | 200 |  |  |

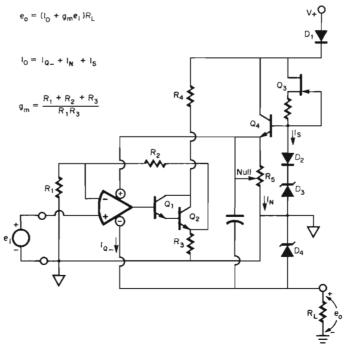

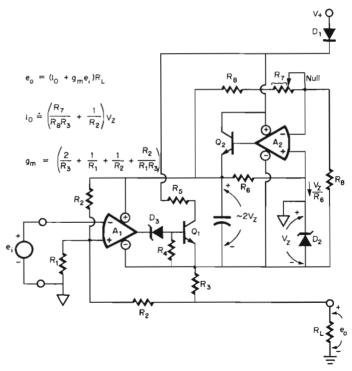

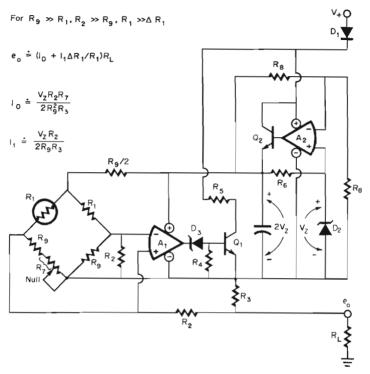

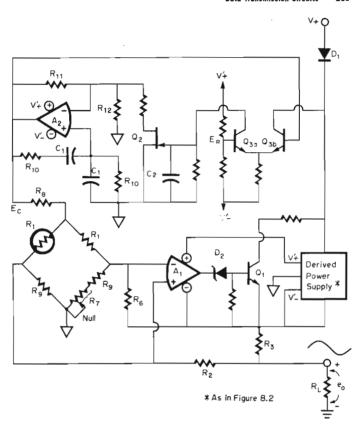

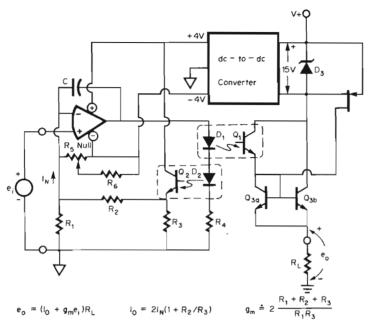

|    | 8.1               | Two-Wire Transmitters 200 8.1.1 General-purpose circuits 202 8.1.2 Specialized two-wire transmitters 208 |     |  |  |

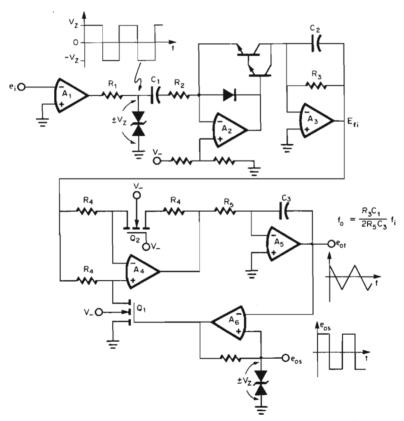

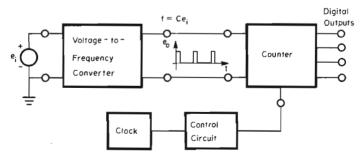

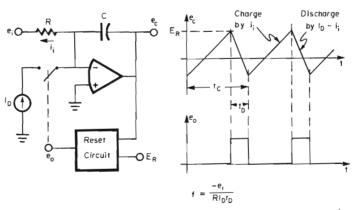

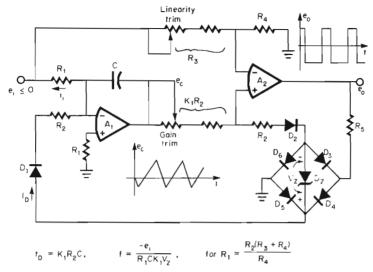

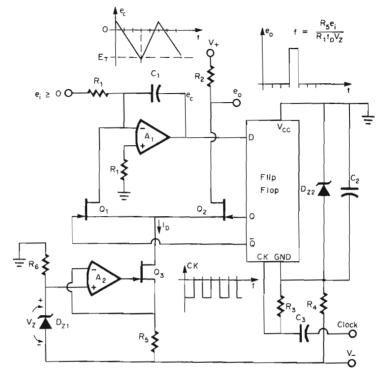

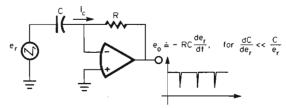

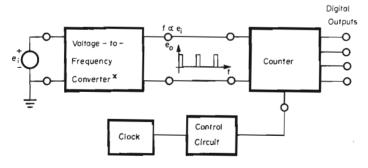

|    | 8.2               | Voltage-to-Frequency Converters 212                                                                      |     |  |  |

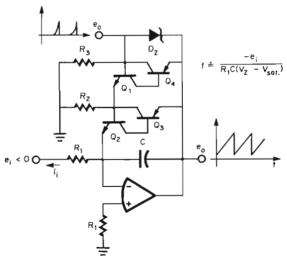

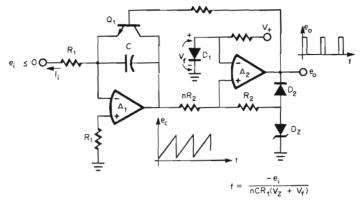

|    |                   | 8.2.1 Moderate-precision configurations 214 8.2.2 High-precision voltage-to-frequency converters 217     |     |  |  |

|    |                   | 5.2.2 High-precision voltage-to-frequency converters 217                                                 |     |  |  |

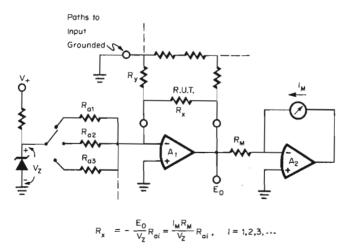

| 9. | TEST              | AND MEASUREMENT CIRCUITS                                                                                 | 224 |  |  |

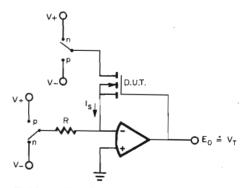

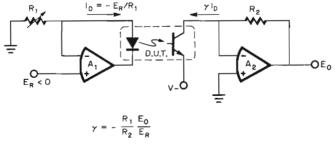

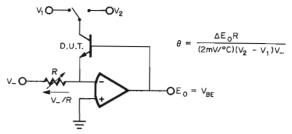

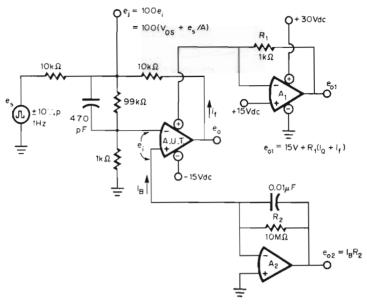

|    | 9.1               | Active Component Test Circuits 224 9.1.1 Transistor test circuits 225                                    |     |  |  |

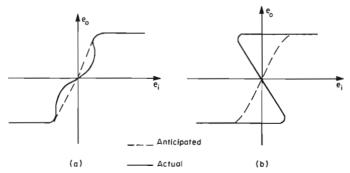

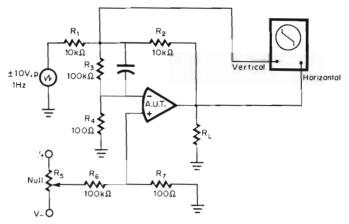

|    |                   | 9.1.2 Operational amplifier test circuits 227                                                            |     |  |  |

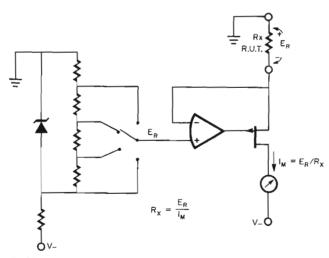

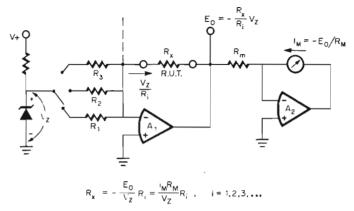

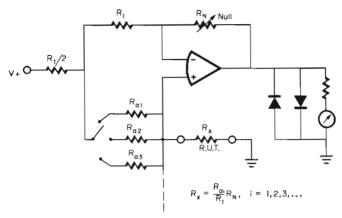

|    | 9.2               | Ohmmeters 231 9.2.1 Conventional ohmmeters 232                                                           |     |  |  |

|    |                   | 9.2.2 Ohmmeters for embedded resistors 235                                                               |     |  |  |

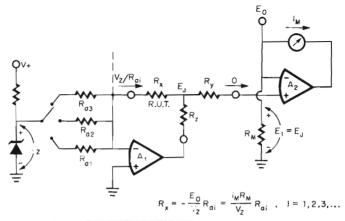

|    |                   | Capacitance Measurement Circuits 237                                                                     |     |  |  |

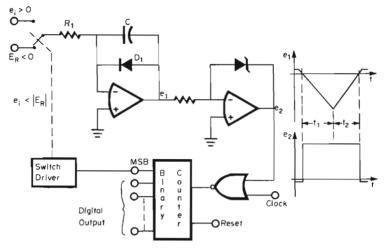

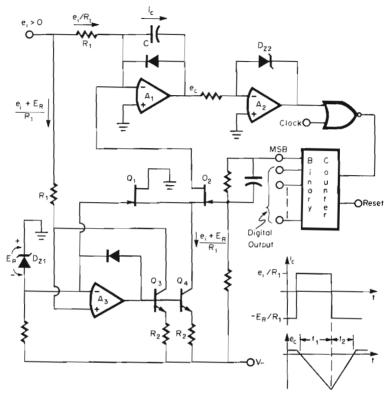

|    | 9.4               | Signal Measurement Circuits 241<br>9.4.1 Digital voltmeters 241                                          |     |  |  |

|    |                   | 9.4.2 Ammeters 245                                                                                       |     |  |  |

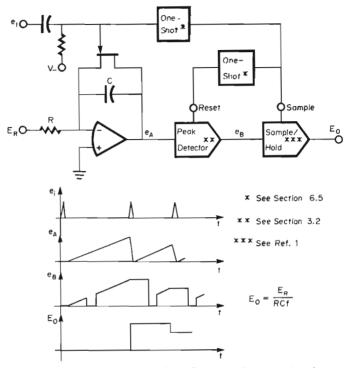

|    |                   | 9.4.3 Frequency measurement circuits 247                                                                 |     |  |  |

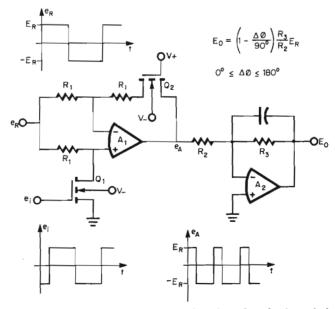

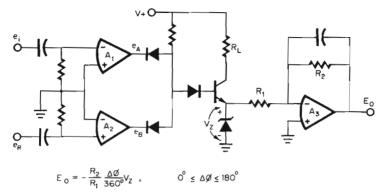

|    |                   | 9.4.4 Phase detectors 251                                                                                |     |  |  |

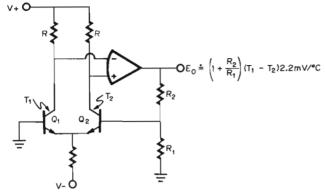

|    | 9.5               | Electronic Thermometers 254                                                                              |     |  |  |

|    | Glossaru 258      |                                                                                                          |     |  |  |

|    |                   |                                                                                                          |     |  |  |

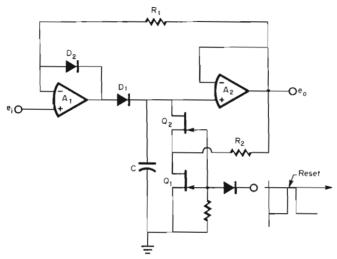

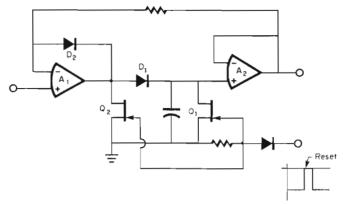

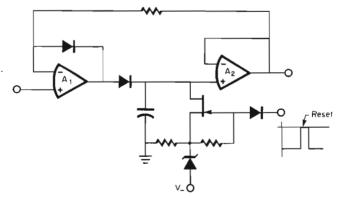

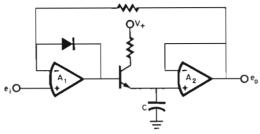

|    | Index 263         |                                                                                                          |     |  |  |

### **PREFACE**

In the continuing evolution of analog electronics, circuit designers have originated and perfected a wide variety of operational amplifier realizations for electronic functions. These versatile amplifiers have become a basic component applied in varied engineering requirements for instrumentation, control, and simulation. Previous circuit applications have been described in the McGraw-Hill/Burr-Brown books Operational Amplifiers: Design and Applications and Applications of Operational Amplifiers: Third-Generation Techniques.† Further developments in the operational amplifier art have generated a new set of implementations of electronic functions, and they are presented in this book.

Intended as a companion volume to the above publications, this book again presents operational amplifier applications in a form that permits ready adaptation to specific uses. Rather than limiting the applications to specific components and associated performance ranges, this book relays circuits in a general form with discussion of the circuit operation, critical component requirements, and related performance limitations. From such coverage, the reader can rapidly define the characteristics of components required to meet his specific application, or he can acquire insight into

† J. Graeme, Applications of Operational Amplifiers: Third-Generation Techniques, McGraw-Hill Book Company, New York, 1973.

<sup>&</sup>lt;sup>o</sup> G. Tobey, J. Graeme, and L. Huelsman, Operational Amplifiers: Design and Applications, McGraw-Hill Book Company, New York, 1971.

circuit operation needed to modify the circuit for a related function. Use of the applications as presented does not require extensive electronics background because the expressions defining circuit operation and errors involve only simple engineering mathematics. From these expressions, one can select specific circuit components for the many uses throughout the engineering discipline without need for specialized electronic experience. To further aid general engineering use, a glossary is included at the end of the book.

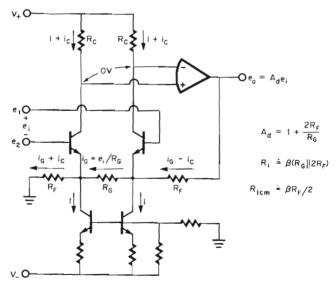

So as to be a convenient reference in implementing electronic functions. the book is organized by circuit function. Applications for similar requirements are grouped together so that one can review alternative approaches in selecting the most appropriate technique for a given requirement. Grouped in Chapter 1 are general amplifier techniques for reducing error, boosting performance, and applying variable feedback networks. Chapter 2 summarizes the most recent implementations of specialized amplifiers for instrumentation, motor control, clamping, and current-source control. Signal analyzer groupings in Chapter 3 include comparators, peak detectors, and voltage discriminators. For signal conditioning requirements, Chapter 4 details selected voltage regulators, active filters, and frequency multipliers. Chapter 5 expands upon the widely used absolute-value circuits or precision rectifier approaches and means for their performance improvement. Included in Chapter 6 are newer techniques for generation of sine waves, square waves, triangle waves, ramp trains, pulse trains, staircase waveforms, and timed duration pulses. More powerful analog computation circuits for addition, subtraction, integration, differentiation, multiplication and division, and trigonometric and other functions are presented in Chapter 7. Two-wire transmitters and voltage-to-frequency converters for remote data acquisition and data conversion are covered in Chapter 8. Concluding the applications described are the test and measurement circuits of Chapter 9, which permit measurement of additional transistor and amplifier characteristics and measurement of resistance, capacitance, voltage, current, frequency, phase, and temperature.

I am once again grateful for the manuscript review by Donald R. McGraw, whose exceptional breadth of knowledge in the operational amplifier techniques resulted in many improvements. My appreciation is expressed to Burr-Brown Research Corporation, whose furthering of the analog-function technology provided the catalyst for derivation of much of the circuitry presented. My thanks to Fran Baker for her dedicated typing of the manuscript and occasional ntertaining editing. Also, thanks to my wife Lola for again producing precise, visually pleasing illustrations and for providing the rewarding feeling of mutual involvement in preparing this book.

### DESIGNING WITH OPERATIONAL AMPLIFIERS

1

### **GENERAL AMPLIFIER TECHNIQUES**

Of common use to the wide variety of operational amplifier applications are general techniques for enhancing performance and controlling closed-loop characteristics. Major circuit errors can be removed through techniques that compensate input offset voltage and input bias currents. Source loading errors can be avoided by making use of circuits that boost the input impedance presented by an operational amplifier circuit to a signal source. With a given operational amplifier an expanded range of functions is available through the use of output power boosting and through full-power response boosting. Utility is further extended by the ability to vary the effect of operational amplifier feedback networks. Generally, this involves continuous or switched variation of closed-loop gain, but the same control techniques also permit variation of response characteristics through switching a circuit function. Described in this chapter are techniques for achieving these results that can be applied to a wide range of operational amplifier applications.

### 1.1 DC Error Reduction

Input offset voltage and input bias currents create the major dc errors in operational amplifier circuits; so control of these characteristics can offer significant dc error reduction. For wideband operational amplifiers,

the input offset voltage and its drift are generally quite large relative to more general-purpose amplifiers. The higher offset voltage is generally a result of optimization of response speed. Means are available for reducing that error voltage and drift to the same low levels available with low-drift operational amplifiers. Described below are techniques for using such low-drift operational amplifiers to provide a continuous offset null for wideband amplifiers or any other amplifier having high input offset voltage and drift. Following that description, techniques are presented for compensation of input bias current errors or compensation of the current itself. These latter techniques are derived for noninverting operational amplifier configurations where input currents produce more significant errors with the high impedance, or capacitive sources best monitored with these configurations.

1.1.1 Continuous input offset voltage null Input offset voltage and its drift are characteristically large for wideband operational amplifiers because of design compromises made for faster response. Similarly, low-drift operational amplifiers generally have slow response because their design has been optimized for low drift at the expense of response speed. This speed-accuracy compromise can be circumvented by combining a wideband amplifier with a low-drift one. Together, the amplifiers form a low-drift wideband operational amplifier having the best characteristics of both, as well as greatly increased open-loop gain.

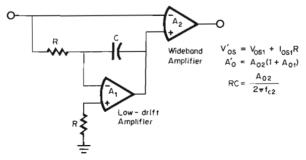

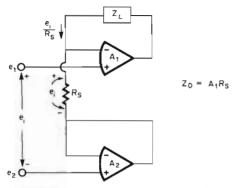

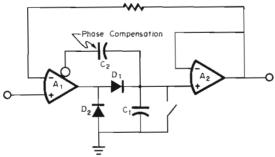

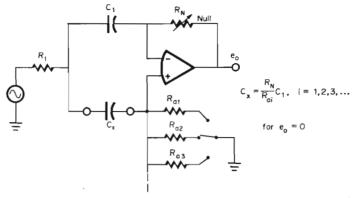

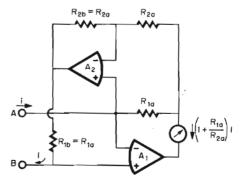

The two amplifiers are connected so that the wideband one controls response and the low-drift one determines input offset voltage. For inverting operational amplifier applications, the amplifiers are connected as in Fig. 1.1. As shown, the low-drift amplifier  $A_1$  performs as an integrator controlling the voltage at the noninverting input of wideband amplifier  $A_2$ . The integrator senses the input offset voltage of  $A_2$  and develops a correction voltage to remove it. Then, the only remaining input offset voltage will be that due to the low-drift amplifier  $A_1$ , which is

Fig. 1.1 Low input offset voltage and drift are provided by an integrator for wideband operational amplifiers to be used in an inverting configuration.

$$V_{os}' = V_{os1} + I_{os1}R$$

and the composite amplifier drift is

$$\frac{\Delta V_{OS}'}{\Delta T} = \frac{\Delta V_{OS1}}{\Delta T} + \frac{\Delta I_{OS1}}{\Delta T} R$$

As connected, the continuous offset null circuit of Fig. 1.1 is a feed-forward structure. High-frequency signals are fed forward around the bandwidth-limited amplifier to the wideband one; so the full bandwidth of  $A_2$  is retained in the composite amplifier. The resulting gain and phase compensation requirements follow from feedforward amplifier theory.<sup>2</sup> At low frequencies, both amplifiers contribute gain as expressed by

$$A'_0 = A_{02}(1 + A_{01})$$

Accompanying the added gain is an additional phase shift with the potential for instability under feedback. To ensure frequency stability and optimize transient response, feedforward phase compensation is chosen for a continuous —6 dB per octave frequency response rolloff. This is achieved by setting the unity-gain crossover of the integrator at the same frequency as the first open-loop pole of the wideband amplifier. Because the integrator frequency response is controlled by its feedback elements R and C, these elements serve as the phase compensation for A<sub>1</sub>. For unity integrator gain at the frequency of the first pole of A<sub>2</sub>,

$$RC = \frac{A_{02}}{2\pi f_{c2}}$$

Here the first pole is represented in terms of the normally specified characteristics of open-loop gain  $A_{02}$  and unity-gain crossover frequency  $f_{c2}$ .

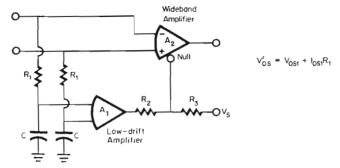

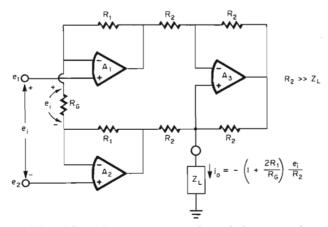

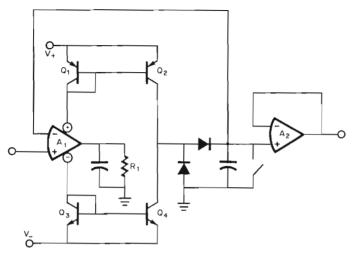

For noninverting or differential operational amplifier connections, an alternative approach is available for continuous input offset voltage null. The previous circuit is not suited for such connections because one amplifier input is committed to the offset correction signal. To leave both inputs available for signal or feedback, the offset correction amplifier can instead drive the offset null terminal of the wideband amplifier, as in Fig. 1.2. Again the low-drift amplifier  $A_1$  senses the input offset voltage of the wideband amplifier and develops a nulling correction signal. Any change in  $V_{0S2}$  will be followed by an appropriate correction signal; so offset drift with temperature and time is continuously compensated for. The only remaining input offset voltage and drift will be due to the dc input errors of the low-drift amplifier:

$$\begin{split} V_{\text{OS}}' &= V_{\text{OSI}} + I_{\text{OSI}} R_{\text{I}} \\ \frac{\Delta V_{\text{OS}}'}{\Delta T} &= \frac{\Delta V_{\text{OSI}}}{\Delta T} + \frac{\Delta I_{\text{OSI}}}{\Delta T} R_{\text{I}} \end{split}$$

### 4 Designing with Operational Amplifiers

Fig. 1.2 For noninverting or differential input applications of wideband amplifiers, continuous input offset voltage null is provided by a low-drift amplifier that drives the wideband amplifier null control in response to any input offset.

Connections between the two amplifiers are made through input filters and a null control voltage divider. The low-pass filters provide phase compensation and block high-frequency signals that might unbalance the low-drift amplifier. Input interconnection polarity is determined by the signal phase relationship of the null terminal with respect to the inputs of A<sub>2</sub>. If the inputs are correctly phased, offset will be driven to zero; otherwise it will be driven away from zero.

Also generally required for interconnection is the level-shifting voltage divider formed with  $R_2$  and  $R_3$ . This divider ensures that the output voltage of  $A_1$  will remain in its linear operating range even though the nominal potential of the null point is generally near one power-supply level. That supply voltage  $V_S$  is used to bias the divider for any required level shift.

Also provided by the circuit of Fig. 1.2 are increased open-loop gain and common-mode rejection. Low-frequency gain is boosted by the signal drive of the offset null point. As with the last circuit, the gain is added in a feedforward manner, and the added gain equals the open-loop gain of  $A_1$  times the gain of  $A_2$  from its null point to its output. Low-frequency common-mode error signals of the inputs of  $A_2$  are also sensed by  $A_1$ ; so a common-mode rejection signal is supplied to the null point as well. This feature is also highly beneficial because common-mode rejection is typically sacrificed with the other input characteristics in optimizing bandwidth.

**1.1.2 Input bias current compensation** The dc error created by operational amplifier input bias current is readily compensated in inverting amplifier applications. In these applications a compensation resistor is placed in series with the noninverting amplifier input, where it develops a compensation voltage with current flow in that input.<sup>3</sup> However, this technique offers little for most noninverting amplifier applications. A major ad-

vantage of noninverting configurations is the high input impedance the present to a source, making possible the monitoring of high impedance sources or holding capacitors. Flow of input bias current in such source is often the dominant source of dc error for the noninverting operationa amplifier. Described below are four techniques for compensating this error by impedance matching and by direct compensation of the input bias current.

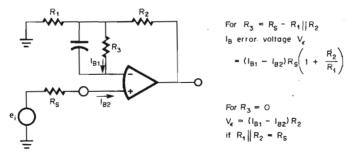

By matching the resistance of the feedback network to the source re sistance, compensating error voltages are developed by the two input bias currents, as illustrated in Fig. 1.3. The desired match is achieved by either inserting a compensation resistor R<sub>3</sub> or by choosing R<sub>1</sub> and R<sub>2</sub> so that their parallel combination equals the source resistance. Then, the does not produced by the input current is associated with the difference between the two currents for typically an order of magnitude less error.

The need for the separate compensation resistor  $R_3$  occurs when  $R_1$  and  $R_2$  cannot be made large enough for the desired compensation without sacrificing precision. Precise resistance is not as critical for the compensation of  $R_3$  as it is for the gain set by  $R_1$  and  $R_2$ . When  $R_3$  is used, it should be capacitively bypassed as shown to preserve frequency stability. Without bypass  $R_3$  forms a low-pass filter with the amplifier input capacitance resulting in increased phase shift in the feedback loop.

Where the source is capacitive rather than resistive, the same compensation cannot be used to remove the error of input bias current. Capacitive sources occur in many sample-hold circuits and peak detectors where a noninverting operational amplifier monitors the voltage stored on a capacitor. In such applications, the input bias current drains the capacitor, producing much of the circuit droop error. Here the need is for a direct compensation of the input bias current. This can be achieved with bootstrapping feedback or with an externally supplied compensating current.

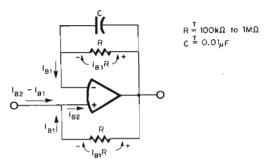

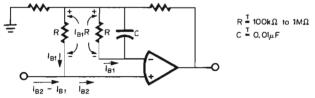

For a voltage follower, the bootstrapping feedback is applied as in Fig.

Fig. 1.3 For noninverting operational amplifier connections the dc error produced by input bias current can be greatly reduced by matching the feedback resistance to the source resistance.

Fig. 1.4 The input current of a voltage follower can be reduced to the level of the input offset current through a bootstrapping feedback.

1.4. Here the circuit input current is reduced to essentially the difference between those of the operational amplifier at the expense of an output offset. Current from the inverting amplifier input flows through a resistor R to develop an output voltage  $I_{B_1}R$  for the bootstrap feedback. This voltage constitutes an output offset, but it biases the bootstrap feedback resistor to the noninverting input. As long as this voltage is much greater than the amplifier input offset voltage, it is essentially the voltage impressed on the bootstrap resistor. By making the bootstrap resistor equal to the feedback resistor, the bootstrapping current is made equal to  $I_{B_1}$ . This current largely cancels the circuit input current because the two amplifier input currents tend to match.

To make use of this technique, it is desirable to null the amplifier input offset voltage, and it is necessary to bypass the negative feedback resistor. The nulling reduces error introduced by the amplifier input offset voltage in the feedback current, and it makes possible the use of a smaller bootstrap bias voltage for less output offset. Typically, an adequate bootstrap bias is developed with a resistance from 100 to 1,000 k $\Omega$ . Such resistance in the negative feedback loop must be heavily bypassed with about 0.01  $\mu F$  to preserve frequency stability and transient response.

The input current compensation technique of Fig. 1.4 can also be applied to the general noninverting amplifier, although the associated output offset

Fig. 1.5 A bootstrapping feedback can also be used to reduce the input current of a noninverting amplifier to the level of its input offset current.

can become large. Once again, the resistor R is inserted in series with the inverting input to develop a bootstrap bias voltage in Fig. 1.5. That voltage biases a matching resistor to supply the compensation current to the signal input. Compensation reduces the circuit input current to the level of the amplifier input offset current, as long as the amplifier input offset voltage does not significantly add to the bias on the bootstrap resistor. While this suggests that a large bootstrap bias voltage is desirable, the effect of that bias on the output offset must be considered. For the noninverting amplifier the bootstrap voltage is amplified by the circuit gain. Thus, it is desirable to carefully null the input offset voltage and keep the bootstrap bias small.

To avoid the offsetting effect of the bootstrap compensation technique, the input compensation current can be supplied by an external source.

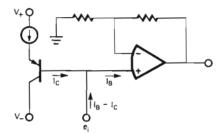

Fig. 1.6 Input bias current compensation from the base current of an external transistor ensures temperature tracking compensation.

For operational amplifiers using bipolar input transistors, a drift tracking compensation can be supplied from the base of an external transistor as in Fig. 1.6. By adjusting the current source, the compensation current  $I_C$  can be made to null the input bias current  $I_B$ . Thermal drift in the compensation transistor base current will tend to track that of the amplifier input transistor; so  $I_C$  will follow the drift of  $I_B$ .

Tracking is approximate because the compensation transistor cannot be matched to the amplifier input device, especially because they are of an opposite conductivity type. A pnp compensation transistor is required to compensate the base current of an npn input transistor, and vice versa. Additional compensation error arises from the voltage sensitivity of the current source. As signal swing varies the voltage on the current source, some change is induced in the current level. This represents a reduction in input impedance equal to a shunt of the current-source output resistance times the  $\beta$  of the compensation transistor.

### 1.2 Boosting Input Impedance

High input impedance contributes significantly to the accuracy with which operational amplifiers monitor signals, and numerous techniques are

### 8 Designing with Operational Amplifiers

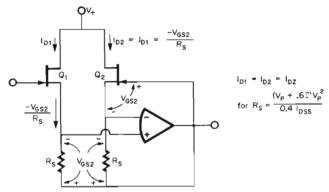

Fig. 1.7 Source-follower buffers at a voltage-follower input can be biased with resistors rather than current sources when a bootstrapping bias is used to remove signal swing from the resistors.

employed to boost that impedance.<sup>3</sup> Two others are presented here that provide bootstrapped FET (field-effect transistor) buffering of a voltage follower and permit connection of an inverting-only operational amplifier in noninverting configurations. The noninverting connection of such amplifiers achieves a dramatic increase in circuit input impedance because the signal then drives the amplifier input direct, rather than a summing resistor.

With FET buffering, the input impedance of a voltage follower is boosted to those levels limited by stray leakage resistance. A simple, high-performance approach to this buffer is the bootstrapped bias configuration shown in Fig. 1.7. In this circuit, the FET current bias is provided by resistors, but the FET currents are made immune to signal swing by bootstrapping bias from the amplifier output. Normally, source followers such as  $Q_1$  and  $Q_2$  would be biased from resistors connected to the negative supply. However, signal swing would then be directly impressed on these resistors, resulting in severe variation in the FET currents. Such current variations induce somewhat different changes in the gate-source voltages of  $Q_1$  and  $Q_2$ , because the FETs cannot be perfectly matched. The result is a differential error signal that greatly degrades the gain accuracy of the voltage follower.

To avoid this error, source-follower buffers are often biased from current sources. This added circuit complexity is avoided with the bootstrap bias of Fig. 1.7 because the signal swing is removed from current-setting resistors  $R_s$ . Only the gate-source voltage of  $Q_2$  is impressed on the source resistors, and this is sufficient for biasing. No other voltage bias is required, and it is this self-biasing capability of FETs that makes this technique possible. The bootstrapping connects the source resistor of  $Q_2$  between

the gate and source of that FET to fix its bias voltage. Essentially the same voltage is established on the other source resistor because near-zero voltage resides between the amplifier inputs. Thus the FET currents are

$$I_{D1} = I_{D2} = \frac{-V_{GS2}}{R_S}$$

No significant change in this current level occurs with signal swing because the voltage-follower output drives the source resistors with a signal that equals the one impressed at the input.

The exact level of  $I_{D1}$  and  $I_{D2}$  can be predicted from the FET pinchoff voltage  $V_P$  and zero bias current  $I_{DSS}$ . For a given value of  $R_S$  the biasing currents reach an equilibrium level where the gate-source voltage and source current of  $Q_2$  are compatible. Generally, it is desirable for this current to be the zero temperature coefficient level  $I_{DZ}$ , where the gate-source voltage  $V_{GSZ}$  is independent of temperature. These zero-drift bias levels are related to FET characteristics by

$$\begin{split} I_{DZ} &\doteq \frac{0.4 I_{DSS}}{V_{\text{P}}^2} \\ V_{\text{CCZ}} &\doteq V_{\text{P}} + 0.63 V \qquad V_{\text{P}} < 0 \end{split}$$

For the buffer of Fig. 1.7 a voltage equal to  $V_{GSZ}$  impressed on  $R_S$  will establish current equal to  $I_{DZ}$  if

$$R_S = \frac{(V_P + 0.63) V_P^2}{0.4 I_{DSS}}$$

$V_P < 0$

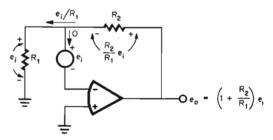

Another technique provides high input impedance with single-ended input operational amplifiers such as most chopper-stabilized and feed-forward amplifiers, if the signal source can be floated. This approach is particularly useful for such inverting-only amplifiers because they cannot be connected in the noninverting configurations to achieve high circuit input impedance. Instead, these amplifiers can be connected in the noninverting configuration of Fig. 1.8. In this circuit the signal is connected

Fig. 1.8 High circuit input impedance with inverting-only operational amplifiers is achieved by connecting the signal source between the feedback network and the amplifier input.

directly to the high impedance input of the operational amplifier rather than to the summing resistor of an inverting configuration. This high impedance input draws very little current; so the signal source is lightly loaded.

Feedback forces the inverting amplifier input to essentially ground potential to produce the output signal shown. With zero voltage at that input, the feedback voltage on R<sub>1</sub> must equal the input signal e<sub>1</sub>. Then, the feedback current must be e<sub>1</sub>/R<sub>1</sub>, and the signal on R<sub>2</sub> will be R<sub>2</sub>e<sub>1</sub>/R<sub>1</sub> for the output indicated. To preserve this response, care must be taken to avoid noise pickup on the feedback path through the signal source.

### 1.3 **Power Boosters**

Most operational amplifiers lack the output current and voltage capability needed to drive electromechanical devices, such as relays, motors, and speakers. For these applications a variety of circuits have been developed to boost output current and voltage.3 Simplified current and voltage boosters are described below.

1.3.1 Current boosters Complementary emitter followers provide the simplest bipolar current boosting for an operational amplifier. However, it is generally necessary to add considerable circuitry to bias such emitterfollower pairs in avoiding crossover distortion. That distortion occurs at the zero crossing of the output signal if one emitter follower must be turned off and the other turned on as the output current polarity reverses. Because some nonzero time is required to drive the transistors on and off, there is a portion of the output swing where neither transistor is on, and the output remains at zero.

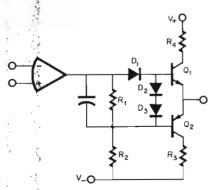

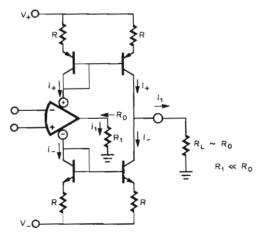

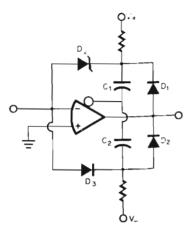

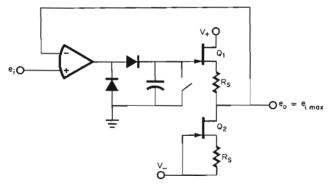

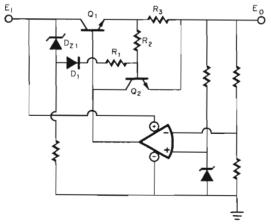

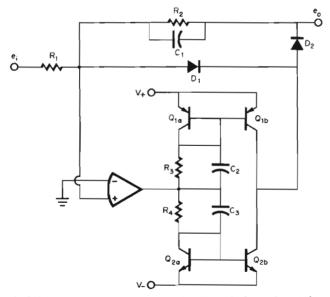

Such distortion is removed by class A-B biasing of the complementary emitter followers as in Fig. 1.9. Diodes D2 and D3 provide a bias voltage

Fig. 1.9 Current sources are not required to ensure adequate base current supply under voltage swing when R<sub>1</sub> is added to provide a current path from the amplifier to Q2.

which ensures that both transistors are on at the zero crossing. However, the resistor bias of such diodes is not generally adequate. If  $R_2$  alone were used, it would be the sole source of base drive current for  $Q_2$ . The current available through  $R_2$  varies with the output voltage, and at the negative swing extreme it is greatly reduced. Therefore, it is normally necessary to use a current source rather than a resistor to supply current to the biasing diodes.<sup>3</sup>

Instead, the resistor  $R_1$  of Fig. 1.9 can be added so that the operational amplifier output current is also available to drive the base of  $Q_2$ . As the base current of  $Q_2$  increases, it gradually diverts current from  $R_1$  until the voltage on  $R_1$  is zero. Any further base current demand will result in an amplifier output voltage below that of the base, and this reverses the direction of current in  $R_1$ . Now current from the amplifier is supplied through  $R_1$  to the base of  $Q_2$ . Since the transition in  $R_1$  current is gradual, no abrupt distortion is induced. The reversal in voltage on  $R_1$  also reverse-biases  $D_1$ , which serves to protect  $Q_1$  from damaging emitter-base breakdown. That diode may not be required if the reversed voltage on  $R_1$  is sufficiently limited, as determined by the point of transition to reverse voltage.

Resistor  $R_2$  is chosen to set the transition point, and  $R_1$  sets the booster quiescent current. Generally,  $R_2$  is selected for a transition point at an output voltage and current of about one-half the maximum desired. Beyond that point, little increase in voltage is required on  $R_1$  to supply base current to  $Q_2$  for the remaining desired output current. Greater voltage on  $R_1$  would then only occur under output short circuit, where  $D_1$  would be needed to protect  $Q_1$ . Also required under this short-circuit condition is an output current limit for each transistor; this is provided by  $R_3$  and  $R_4$ . The latter resistors cause the transistors to saturate under excessive current flow. In this saturated mode the transistor current gains and the power dissipations are greatly reduced.

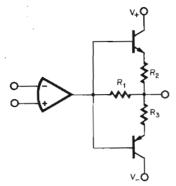

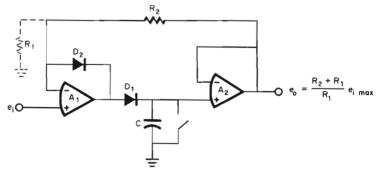

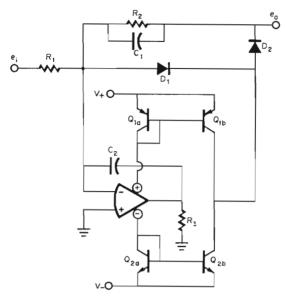

An even simpler low-distortion current booster is available if somewhat higher output resistance at low current is acceptable. This current booster has basically class B bias; so there is no quiescent drain from the booster. But the circuit is connected for continuous supply of output current through the zero crossing, as shown in Fig. 1.10. Near the output zero crossing, both transistors are off, but output current continues to be supplied through R<sub>1</sub> from the operational amplifier. No current boosting is then available, but it is not required for grounded loads when the voltage is small. As the output moves away from its zero crossing, load current is drawn through the resistor R<sub>1</sub>, whose voltage gradually turns on one of the transistors to provide additional output current.

This transition will be gradual without crossover distortion as long as the amplifier is not forced into slew-rate limiting by the transition. Such a

Fig. 1.10 Crossover distortion is removed from a class B current booster by a direct load current supply path through R<sub>1</sub>.

rate-limited condition can result if the load resistance is small compared with R<sub>1</sub>, such that the amplifier output swing would be much larger than that of the power booster during the transition. If the amplifier becomes rate-limited during the transition, it introduces a delay in booster output rise that appears as crossover distortion. To avoid this distortion, R<sub>1</sub> and the load resistance should be no smaller than about one-tenth the rated load of the operational amplifier. This permits current booster gains up to 10.

Because the operational amplifier output current is the source of bias to the emitter followers, the amplifier current limit serves to limit the booster current as well. If the operational amplifier output current reaches its limit level, the voltage on R<sub>1</sub> is also limited. That voltage determines the maximum bias for the transistors and their emitter resistors, and so the maximum booster current.

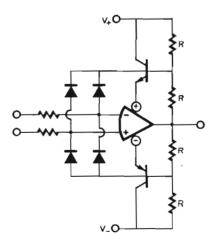

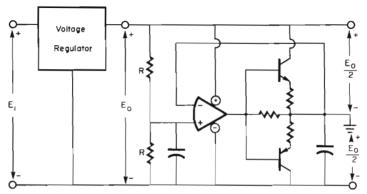

1.3.2 Voltage boosters To increase the output voltage swing of an operational amplifier, a gain stage can be added to the amplifier, or its power supplies can be bootstrapped from the output. Addition of a gain stage is fairly straightforward, and this stage can be greatly simplified by using the power-supply current drains of the amplifier for the bias and signal drive of this stage. By bootstrapping the amplifier power supplies, output voltage swing can be doubled as in Fig. 1.11. In this circuit the voltages supplied to the amplifier power-supply terminals by the emitter followers are nominally one-half those of the actual power supplies. These amplifier supply voltages are bootstrapped from the amplifier output so that they track output swing. As a result, the amplifier output may swing to twice its normal rated voltage without the total voltage across the amplifier exceeding the maximum allowable. Essentially, this technique makes use of the amplifier total peak-to-peak output swing capability for each output

swing polarity. In normal operation the maximum instantaneous output voltage of an operational amplifier is only one-half the total swing capability, because the other half of this capability is devoted to supporting a large biasing power-supply voltage. With the bootstrapping technique, no such bias is supported when it is not required for signal swing.

A potential failure of the above bootstrap operation is input overload. Fast-rising input signals could raise the amplifier inputs to high voltages before the amplifier output could respond to adjust the voltages at the amplifier supply terminals. Such overload would occur whenever the operational amplifier was forced into rate limiting unless input protection is incorporated. In the circuit of Fig. 1.11 resistors and diodes are added to clamp the amplifier inputs at the levels of the amplifier power-supply voltages.

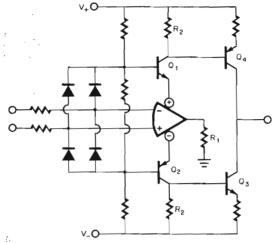

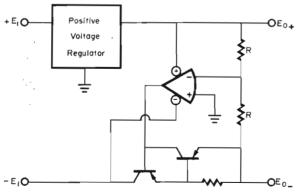

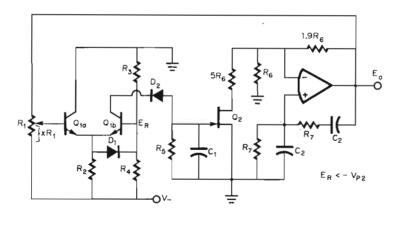

Another way to increase amplifier output voltage swing is to add a gain stage. Normally, such a gain stage would be driven from the amplifier output, but a simpler circuit results if the added stage is driven as in Fig. 1.12. Here the signal, as well as the bias, is coupled to the gain stage through the power-supply current drains of the operational amplifier. No separate bias circuit is required. Bias for both the operational amplifier and the gain stage  $Q_3$  and  $Q_4$  is provided via  $Q_1$  and  $Q_2$ . The latter transistors would normally be needed to supply reduced supply voltage to the operational amplifier. In this case, they also provide a source of biasing current and voltage level shifting to the bases of  $Q_3$  and  $Q_4$ .

Signal current through the added stage is generated by operational amplifier output swing on resistor  $R_1$ . Any current supplied to  $R_1$  must flow through one of the amplifier power-supply terminals, where it is

Fig. 1.11 Bootstrapping the powersupply voltages applied to an operational amplifier doubles output swing capability.

Fig. 1.12 An output voltage boosting stage without need for separate biasing is made possible by driving the stage with the power-supply line currents of the operational amplifier.

coupled to the gain stage. This coupling to the bases of  $Q_3$  and  $Q_4$  occurs with a voltage gain on the order of  $R_2/R_1$ . Voltage gain from there to the output is load-sensitive since the open-loop output resistance is quite high. Closed-loop output resistance, however, as well as any response nonlinearity, is greatly reduced by the feedback-loop gain.

Other characteristics of this circuit include the ability for current boosting, the lack of need for separate output current limiting, the potential for increased slewing rate, and a need for input protective clamping. By choice of resistors, the circuit can be made to boost output current as well as voltage. Output current limiting will often be provided by the internal limit of the amplifier, because its limited output current corresponds to a limited drive voltage to the gain stage. To preserve large-signal bandwidth with the higher voltage swings, a greater slewing rate is required. This too can be achieved with the circuit of Fig. 1.12. As described in the next section, the rate limiting of the operational amplifier can be avoided until higher frequencies by keeping its output voltage swing small. This is easily achieved by making R<sub>1</sub> small so that only small amplifier output voltage swing is required to develop its rated output current. Input protection is often required to protect the amplifier from the higher signal levels that may accompany higher voltage operation. If the input signals can be large enough to exceed the operational amplifier input ratings, the input clamp diodes and resistors shown should be added.

### 1.4 Boosting Full-Power Response

Operational amplifier large-signal bandwidth is specified as full-power response, and this bandwidth is lower than the small-signal bandwidth by typically a factor of 100. Specialized high-speed operational amplifiers greatly improve this ratio, but it can also be improved with general-purpose amplifiers, as described below. The techniques described boost full-power response by means of an external stage and by feedback modification that lowers the feedback factor without altering closed-loop gain.

The key to the first technique is a reduction in required amplifier output voltage swing. With the reduced voltage swing the slewing-rate limit of an amplifier is not encountered until a higher frequency. To restore full voltage swing to the load, an added gain stage is required, and normally this would require an accompanying increase in phase compensation. Such a phase compensation increase would then generally reduce full-power response to its previous level, or lower, but this can be avoided by decreasing the operational amplifier gain to prevent an overall gain increase.

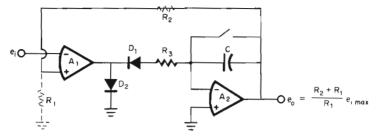

This approach is incorporated in the circuit of Fig. 1.13. For simplified biasing of the added gain stage it is driven by the power-supply drain currents of the amplifier. In this way the quiescent currents of the amplifier provide quiescent bias, and the internal amplifier circuitry performs the voltage level shifting to the bases of the output gain transistors. Amplifier signal current is also conducted through one or the other of the

Fig. 1.13 Full-power response is boosted by lowering operational amplifier output voltage swing and restoring full swing to the new circuit output in a manner that does not increase the overall gain of the circuit.

power-supply terminals, where it drives the gain transistors. For the equal transistor emitter resistors shown, a unity current gain is established from the amplifier to the output transistors. Thus, a current  $i_1$  supplied by the operational amplifier to  $R_1$  will be matched by an equal current supplied to the load  $R_L$ . Then, the gain from the amplifier output to the new circuit output is  $R_1/R_1$ .

To maintain frequency stability without added phase compensation, the operational amplifier gain is reduced by a similar amount. This reduction is easily achieved by making  $R_1$  small compared with the open-loop output resistance  $R_0$  of the amplifier. Then the amplifier open-loop gain is reduced by a factor of  $R_0/R_1$ , and the overall circuit gain is

$$A' \doteq A \frac{R_1}{R_0} \cdot \frac{R_L}{R_1} = A \frac{R_L}{R_0}$$

By making the load resistance comparable to the amplifier output resistance, circuit gain is not significantly changed, and additional phase compensation is not generally required. Full-power response is boosted because only a small amplifier voltage swing is required to supply rated current to the small resistor R<sub>1</sub>. Typically R<sub>1</sub> can be selected so that only one-tenth the amplifier rated-output voltage swing is required to develop full voltage swing at the new circuit output. Where the various requirements above are not readily met, higher full-power response can still be attained if some additional phase compensation is placed in feedback around the operational amplifier.

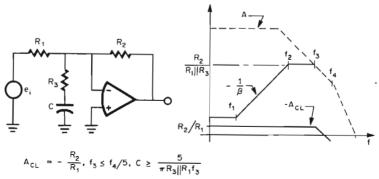

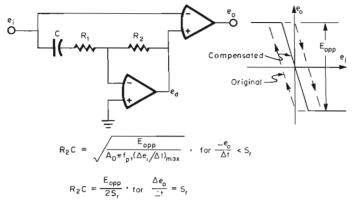

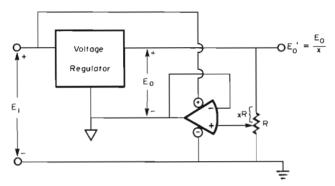

For lower gain applications of externally phase-compensated operational amplifiers, full-power response can also be boosted at some sacrifice in noise performance and gain accuracy. This technique employs feedback connections that lower the feedback factor without increasing closed-loop gain.<sup>5</sup> Only a resistor and a capacitor need to be added to the inverting amplifier configuration for this full-power response boost illustrated in Fig. 1.14. Very little signal is impressed on the added elements R<sub>3</sub> and C; so they do not have a major influence on the amplifier output signal. Thus, the closed-loop gain remains essentially at the level set by R<sub>1</sub> and R<sub>2</sub>.

However,  $R_3$  and C do greatly alter the feedback ratio  $\beta$  of the circuit as represented by the  $-1/\beta$  curve. The feedback ratio is that portion of the output signal fed back to the input, and it is calculated considering the impedance divider from output terminal to the amplifier input terminal. At low frequencies where C appears as an open circuit, the feedback factor is unchanged from

$$\beta_{L} = \frac{R_1}{R_1 + R_2}$$

However, at the high-frequency extreme C appears as a short circuit and

$$\beta_{\rm H} = \frac{{\rm R}_1 \parallel {\rm R}_3}{({\rm R}_1 \parallel {\rm R}_3) + {\rm R}_2} \doteq \frac{{\rm R}_3}{{\rm R}_2}$$

for  ${\rm R}_3 \ll {\rm R}_1$  or  ${\rm R}_2$

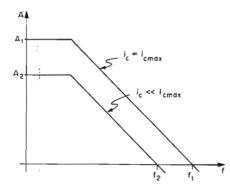

This reduction in feedback factor greatly eases the full-power response-limiting phase compensation, as can be seen from the response plot for  $-1/\beta$ . If  $\beta$  remained constant with frequency, it would intercept the magnitude response curve of the open-loop gain A at a point where the gain curve slope is quite steep. That steep slope correlates with high phase shift through the amplifier,<sup>2</sup> and such a phase shift is sufficient to cause oscillation. The condition for oscillation in a negative feedback system is a 180° phase shift where the feedback-loop gain is unity. That unity-gain point corresponds to the intercept of the  $1/\beta$  curve and the gain magnitude curve, and this is the point at which phase shift must be limited.

Note that the decrease in  $\beta$  moves this critical intercept to a portion of the gain response curve that is much less steep, and thereby where the phase shift is much less. Frequency stability is then ensured without the need for heavier phase compensation, which would greatly decrease full-power response. Without the feedback factor decrease, phase compensation would have to be increased enough to maintain a -6 dB per octave gain slope past the intercept level of the  $R_2/R_1$  line. The lighter phase compensation typically provides an order-of-magnitude increase in full-power response over that available with operational amplifier phase compensation selected for unity-gain applications. Small-signal bandwidth, however, is not increased, as indicated by the response of the closed-loop gain  $A_{CL}$ . This gain response declines with the open-loop gain response, following the intercept of the  $-1/\beta$  curve.

Gain accuracy is commonly reduced by feedback factor decrease. However, this accuracy is largely restored by the greater open-loop bandwidth

Fig. 1.14 Higher full-power response is achieved with phase compensation reductions permitted by a feedback factor decrease that does not alter closed-loop gain.

accompanying the decrease in feedback factor. Without the  $\beta$  decrease the bandwidth of the open-loop gain A would have to be greatly reduced by phase compensation. However, the high-frequency loop gain is preserved by the lighter phase compensation requirement. Low-frequency loop gain is maintained by the use of the coupling capacitor C, which prevents feedback factor reduction at low frequency. To optimize gain accuracy, the coupling capacitor should be carefully chosen to preserve frequency stability without unnecessarily degrading loop gain. The larger the capacitor, the less phase shift it introduces near the critical intercept point at  $f_3$  but the more it reduces the lower frequency loop gain. Loop gain magnitude can be seen from the response plots as the difference between the A and the  $1/\beta$  curves. Capacitor C combines with  $R_1$  to create the  $1/\beta$  response zero at  $f_1$ , and with  $R_3$  to develop the pole at  $f_2$ . For frequency stability,  $f_2$  should be a factor of 10 lower than  $f_3$ . Combining these various relationships defines the requirement for C as

$$C \ge \frac{5}{\pi R_3 \parallel R_1 f_3}$$

For good frequency stability also,  $f_3$  should be about 5 times lower than  $f_4$ . Maximum benefit from this technique is achieved for  $R_3$  much less than  $R_1$  or  $R_2$  so that the high-frequency feedback factor is significantly reduced. This lower value of  $R_3$  would result in high gain to the amplifier input offset voltage, but that is prevented by the coupling capacitor.

Noise performance is more seriously affected by this full-power response-boosting technique. The input noise voltage of the operational amplifier is amplified by a gain of  $-1/\beta$ , which becomes large at high frequency in the curve of Fig. 1.14. As a result, high-frequency amplifier voltage noise is amplified much more than with the conventional operational amplifier feedback network.

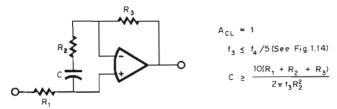

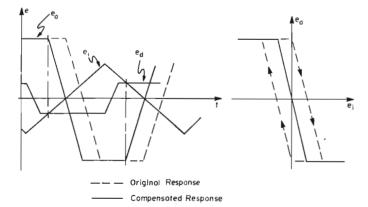

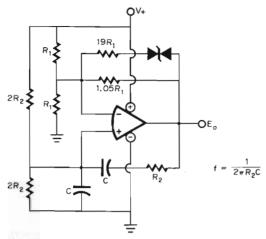

An analogous full-power response-boosting modification can be made to the feedback network of a noninverting amplifier as in Fig. 1.15. This technique is shown for a voltage follower with components added to decrease the feedback factor at high frequency and permit phase compensation reduction. At low frequency the coupling capacitor C appears as an open circuit; so no feedback current is conducted through R<sub>3</sub>, and the negative feedback factor is unity. At a higher frequency where C appears as a short circuit, the negative feedback factor is

$$\beta_{\text{H-}} = \frac{R_1 + R_2}{R_1 + R_2 + R_3}$$

In this case, feedback is also returned to the noninverting input, and the associated positive feedback factor is

$$\beta_{\rm H+} = \frac{R_1}{R_1 + R_2 + R_3}$$

Fig. 1.15 For a voltage follower, increased full-power response is provided by phase compensation reductions made possible by a feedback factor reduction that does not alter closed-loop gain.

The net feedback factor at high frequency is the difference between the positive and negative levels

$$\beta_{\rm H} = \frac{{\rm R}_2}{{\rm R}_1 + {\rm R}_2 + {\rm R}_3}$$

Thus, feedback factor at high frequency can be greatly reduced by making  $R_2$  much less than  $R_1$  or  $R_3$ . The resulting response curves are much like those of Fig. 1.14. Differences from those response curves include a unity feedback factor at low frequency and a unity closed-loop gain up to the rolloff at  $f_3$ . Closed-loop gain remains unity since very little signal is impressed on  $R_2$  and C across the amplifier input. Very little signal current then is developed in the resistors  $R_1$  or  $R_3$ ; so the output signal essentially follows that at the input.

Feedback components required to provide the full-power response boost for the circuit of Fig. 1.15 are selected with the considerations outlined for the preceding circuit. Referring to the response plots accompanying that circuit,  $f_3$  is again chosen to be about one-fifth  $f_4$ , and  $f_2$  is set at about one-tenth  $f_3$ . This requires that

$$C \ge \frac{5}{\pi R_2 f_3}$$

While higher values of C help ensure frequency stability, they also reduce loop gain, and thereby gain accuracy, at intermediate frequencies. As before, the capacitor C also decouples high gain from the amplifier input offset voltage. High-frequency noise receives much greater amplification, as described with the last circuit.

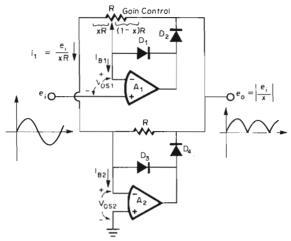

### 1.5 Continuously Variable Gain Control

With potentiometers the closed-loop gain of operational amplifiers can be continuously varied over a wide range. In simplest form, the resulting gain varies nonlinearly with the potentiometer resistance. However, the gain can also be made to vary linearly so that turns-counting poten-

Fig. 1.16 The closed-loop gain of inverting operational amplifier configurations can be varied with only a potentiometer or, where linear control is desired, with a potentiometer and a resistor.

tiometer dials can be used for direct reading of gain setting. Described in this section are the potentiometer-controlled gain configurations commonly used with inverting, noninverting, and differential connections of operational amplifiers. Also presented is a circuit that provides bipolar adjustment of gain for variation of gain through both positive and negative levels.

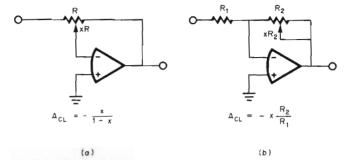

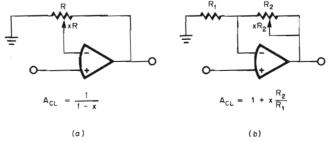

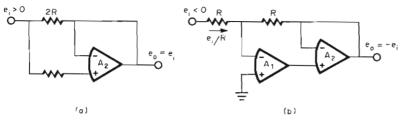

For the inverting operational amplifier connection, the two basic potentiometer gain controls are illustrated in Fig. 1.16. As shown, gain can be controlled with the potentiometer alone or with a potentiometer and a resistor. When only the potentiometer is used, the control function is nonlinear as expressed in Fig. 1.16a. To achieve a linear control, the additional resistor of Fig. 1.16b is required. In both cases, the accuracy of the gain control function expressed is primarily determined by the accuracy of the potentiometer movement. Both circuits require careful interconnection of the potentiometer to the amplifier input to avoid noise pickup and stray capacitance. Stray capacitance introduces phase shift in the feedback loop and can cause oscillation.

Fig. 1.17 Potentiometer control of noninverting amplifier gain is also possible if linear control is not required.

Noninverting operational amplifier configurations do not adapt as readily to linear gain control. The basic potentiometer-controlled gain connections are shown in Fig. 1.17. As indicated, both connections result in a nonlinear gain variation with potentiometer resistance. For linear gain control the noninverting amplifier can be followed by the variable-gain inverting amplifier of Fig. 1.16b, or a differential amplifier can be used. These differential amplifier circuits include that to be presented in Fig. 1.19 or specialized instrumentation amplifier circuits.<sup>3</sup> Generally, the differential amplifier circuits are preferable only where the phase inversion of the above inverting amplifier alternative is not acceptable. Otherwise, lower input impedance or greater circuit complexity results.

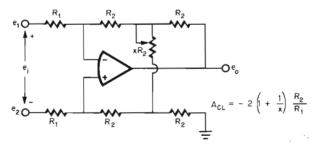

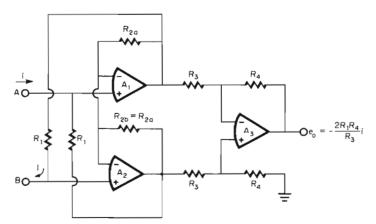

One of the means for attaining linear gain control with a noninverting amplifier response is to use the noninverting input of a difference amplifier having the desired gain control function. Two difference amplifier connections having potentiometer gain control are described below. The simpler circuit has a nonlinear gain control function, but the addition of a second operational amplifier provides linear control for the second circuit. In the simpler case, two resistors and a potentiometer are added to the basic difference amplifier connection<sup>2</sup> as in Fig. 1.18. Here the potentiometer performs as one segment of the two resistor tee networks of the difference amplifier. Because one potentiometer varies the effective resistances of both networks, common-mode rejection is not disturbed by the gain control. If two controls were used to separately vary the two net-

Fig. 1.18 A single potentiometer provides gain control for a difference amplifier without disturbing common-mode rejection when the potentiometer is connected as a common element of two difference tee networks.

works, high common-mode rejection would be difficult to maintain since it is very sensitive to the network resistance match. Common-mode rejection does still require close matching of like resistors, but tolerance error of the potentiometer only results in a gain error.

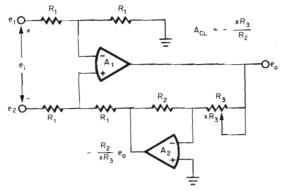

Linear gain control of a difference amplifier response can be developed by simply following a common difference amplifier with the gain-con-

Fig. 1.19 Linear gain control for a difference amplifier results with a gain-controlled inverting amplifier inserted in the difference amplifier feedback loop.

trolled inverting amplifier of Fig. 1.16b, or to avoid cascading amplifiers a gain-controlled inverting amplifier can be connected in the feedback path of a difference amplifier as in Fig. 1.19. This inverting amplifier  $A_2$  attenuates the output signal  $e_0$  to supply a feedback signal. Feedback forces the output signal of  $A_2$  to equal the differential input signal, and it does so by developing the appropriate signal at the output of  $A_1$ . Relating the two amplifier output signals is the gain of the inverting amplifier, and the result is the gain control function expressed. Also added to the feedback are the offset voltage and phase shift of the inverting amplifier. The offset voltage is amplified along with that of  $A_1$  by the net circuit gain. Phase shift introduced by  $A_2$  can degrade frequency stability at lower gain levels.

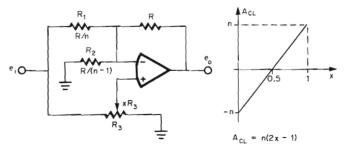

Each preceding gain control technique permits variation of one gain polarity. Operational amplifiers, however, have bipolar voltage swing; so it is sometimes desirable to vary gain through both positive and negative

Fig. 1.20 Gain can be linearly varied through positive and negative levels with a single potentiometer that varies circuit operation from inverting amplifier to noninverting amplifier.

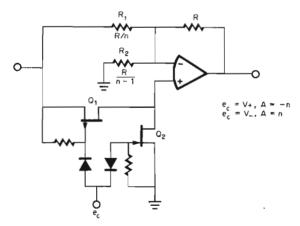

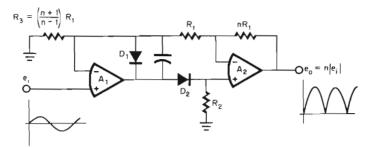

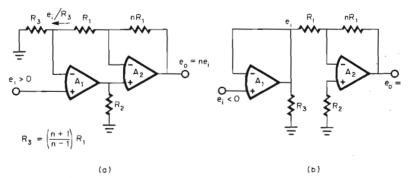

levels. A surprisingly simple operational amplifier connection results in such bipolar gain control by means of a single potentiometer as illustrated in Fig. 1.20. In addition, the gain control function is linear. The potentiometer varies the signal applied to both the inverting and noninverting inputs of the amplifier to achieve both positive and negative gains. At one potentiometer extreme, where x equals zero, the noninverting input is connected to ground; so no signal reaches that input. This condition also holds the voltage across  $R_2$  at zero so that it has no effect on circuit gain. Then, only  $R_1$  and R conduct feedback current, and the circuit performs as a simple inverting amplifier with a gain of -n.

At the other extreme of the potentiometer range, where x equals 1, the input signal is connected direct to the noninverting input. Since feedback maintains near-zero voltage between the amplifier inputs, the inverting amplifier input will also reside at the potential of the input signal. Then, no signal is impressed on R<sub>1</sub>, and feedback current flows only in R<sub>2</sub> and R. As a result, the circuit operates as a noninverting amplifier with a gain of +n. In between the two potentiometer extremes, feedback currents flow in both R<sub>1</sub> and R<sub>2</sub> for operation between that of an inverting amplifier and a noninverting amplifier. The polarity of the net circuit gain depends upon which operating mode is dominant, as determined by the potentiometer setting. Analysis reveals that the potentiometer setting linearly varies gain from -n to +n as plotted. The linearity of this gain control is solely determined by the potentiometer linearity, because resistance-ratio mismatch only affects gain magnitude.

Input resistance and offset voltage can, however, induce greater than normal error with this circuit. The circuit input resistance varies with the potentiometer setting, since the current drawn by  $R_1$  varies with the setting of  $R_3$ . That input resistance varies from  $R_3$ , when  $R_1$  conducts no current, to  $R_3$  in parallel with  $R_1$ , where  $R_1$  supplies its maximum feedback current. The resulting variation in loading on a source can produce an error variation in output similar to that of a nonlinear gain function. To minimize the input resistance variation,  $R_3$  can be made much less than  $R_1$ , but this can make for a low value of input resistance. Larger than normal error also results from the gain provided to the amplifier input offset voltage. Both the inverting and noninverting amplifier paths amplify this offset even though they may not conduct signal current. As a result, the associated output offset is equal to two times the circuit gain times the input offset voltage.

### 1.6 Switched Gain Control

By switching the feedback networks connected to an operational amplifier, the closed-loop gain, or even circuit function, can be varied. Switching can be performed by either mechanical or electronic switches, depending

upon the required control function and accuracy. With the mechanical types there is a choice of manual switches or automatic switching with relays. These switches have very low series resistance for minimal error, but they are relatively slow, and their wiring can degrade performance. Electronic switches are much faster and permit short wiring, but they have significantly greater series resistance. These varied switching limitations govern the circuit switching configuration. Generally, mechanical switches are connected in a configuration that minimizes the effects of noise pickup and stray capacitance from wiring. For electronic switches the circuit is configured to minimize error introduced by switch resistance.

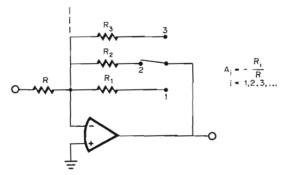

1.6.1 Mechanical gain switching The wiring distance between mechanical switches and an amplifier that they control commonly results in noise pickup and stray capacitance. Because of associated stray signals and capacitance, mechanical switches should not be connected directly to an amplifier input. The high impedance of operational amplifier inputs makes these points susceptible to noise pickup, and the high signal sensitivity of the input results in an amplified noise error. In addition, the high impedance amplifier inputs do not shunt feedback resistance; so stray capacitance forms low-pass filters with the feedback resistance. From this, significant phase shift can be introduced into the feedback loop thereby degrading feedback stability. For these reasons, the preferred point for feedback switching is the amplifier output as in Fig. 1.21. The low output impedance of the amplifier greatly reduces the wiring sensitivity to noise pickup and the phase shift introduced by stray capacitance.

Noise immunity is still less than optimum with the connection of Fig. 1.21, since unused resistors will pick up noise and couple it to the input.

Fig. 1.21 The preferred configuration for operational amplifier gain control with mechanical switches incorporates feedback switching from the amplifier output where impedance is low, resulting in less sensitivity to noise pickup and stray capacitance.

Fig. 1.22 With this switched-gain inverting amplifier connection there are no unused resistors that could pick up noise.

This effect is reduced by mounting the resistors close to the amplifier input so that the wiring to the amplifier is short. Further noise improvement results from capacitive bypass to ground of the switched end of each resistor, but this has other undesirable effects. First, it places increased capacitance load on the amplifier output with potential for frequency instability. Also, such bypass capacitors lower the feedback factor at high frequencies in the same manner described with the full-power response-boosting circuit of Fig. 1.14. As a result of the feedback factor reduction, closed-loop bandwidth and gain accuracy will be reduced unless phase compensation is switched with closed-loop gain.

Another alternative is available for avoiding noise coupling through unused resistors. With the alternative approach, all feedback resistors are used in each gain position so that there are no floating resistors that would pick up noise. For an inverting amplifier this is accomplished with the connection shown in Fig. 1.22. Every resistor is connected in each gain position, and wiring capacitance loads the signal source and amplifier output. However, stray capacitance is not introduced at the amplifier input if the resistors are mounted close to that input. Gain is switched by means of a multiple-contact two-pole slide or wafer switch that connects the various resistors in parallel with either the input resistor or the feedback resistor.

While the resulting gain levels are determined by complex combinations of resistors, the selection of each resistance value is simple. For n different gain levels, n+1 resistors are selected using the expression

$$R_{i+1} = \frac{(A_{i+1} + 1)(A_i - A_{i-1})}{(A_{i-1} + 1)(A_{i+1} - A_i)} R_i$$

where i = 1 to n,  $A_0 = 0$ ,  $A_{n+1} = \infty$ , and  $A_1 < A_2 < A_3 < \ldots < A_n$ . First, a value is arbitrarily assigned  $R_1$ ; then all other resistances are found from this starting point. For gains assigned in ascending order corresponding to

Fig. 1.23 Reduced noise sensitivity for a switched-gain noninverting amplifier is achieved by eliminating open switch positions to feedback resistors.

the number assigned each i of  $A_i$ ,  $R_i$  will be the smallest resistor, and positive values will result for all other  $R_i$ . Even the input current error compensation resistor  $R_0$  can be selected for compensation at all gain levels with the expression

$$R_0 = \left(1 - \frac{1}{A_1}\right) R_1$$

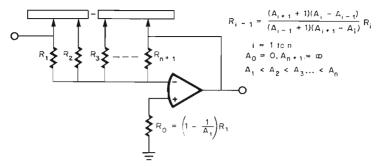

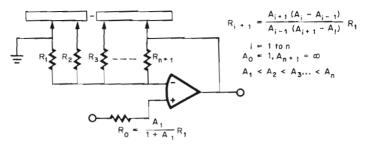

An analogous configuration exists for noise reduction in gain-switched noninverting amplifiers, as shown in Fig. 1.23. In each switch position every resistor is connected either to ground or to the output; so no resistors are left floating to couple noise to the input. Wiring capacitance from the switch is shunted to ground or to the amplifier output. As before, resistor selection begins by choosing an arbitrary value for resistor R<sub>1</sub>; then the remaining resistors are selected by the expression

$$R_{i+1} = \frac{A_{i+1} (A_i - A_{i-1})}{A_{i-1} (A_{i+1} - A_i)} R_1$$

where i = I to n,  $A_0 = 1$ ,  $A_{n+1} = \infty$ , and  $A_1 < A_2 < A_3 < \cdots < A_n$ . Resistor  $R_0$  is chosen for compensation of error due to input bias current by the expression

$$R_0 = \frac{A_1}{1 + A_1} R_1$$

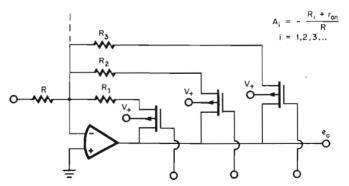

1.6.2 Electronic gain switching While electronic switches lack the low series resistance available with mechanical switches, electronic switching of gain dramatically improves speed and reliability and is capable of direct interface with digital logic circuits. Electronic switches can also be mounted close to an amplifier so that wiring introduces less noise coupling and stray capacitance. This fact makes possible connection of electronic switches to the amplifier input for reduced error from switched resistance, as will be described.

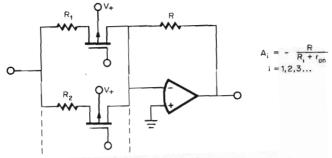

Where the switch remains distant from the amplifier, electronic switches can be connected for gain control in the same configuration presented for mechanical switches in Fig. 1.21. The electronically switched equivalent of this circuit is Fig. 1.24, where MOSFETs (metal oxide semiconductor FETs) replace the mechanical switches. To ensure switch operation, the gate drive and substrate biases must be sufficiently greater than the maximum amplifier output swing. As before, different feedback resistors are connected to the amplifier output for different gain levels. However, in this case the ON resistance  $r_{\rm ON}$  of the MOSFETs can introduce significant gain error, as seen by the gain equation

$$A_{i} = -\frac{R_{i} + r_{ON}}{R} \qquad i = 1, 2, 3, \dots$$

The initial error introduced by  $r_{ON}$  can be compensated for by adjustment of the  $R_i$  resistors, but  $r_{ON}$  varies with signal swing and temperature. Signal voltage at the output varies the gate-source voltages of the MOSFETs, resulting in a modulation of  $r_{ON}$  that introduces distortion.

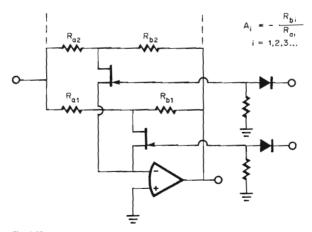

Because electronic switches can be connected to an amplifier input without the long wiring of mechanical switches, it is possible to remove the distortion introduced by signal modulation of the switch ON resistance. This is made possible by the virtual ground of an inverting operational amplifier input and the switch connection of Fig. 1.25. Here the sources of the FETs are connected to that virtual ground; so there will be no signal swing across the gate-source terminals of the FETs. When an FET is in its ON state, the only signal swing across it will be the small voltage developed with the device ON resistance by the current through its input resistor  $R_1$ . That small voltage results in far less modulation of  $r_{ON}$  than experienced with the previous circuit. Further reduction in the

Fig. 1.24 Electronic gain switching can also be performed at the output of an operational amplifier, but a signal-modulated switch resistance will produce distortion.

Fig. 1.25 By connecting gain-switching FETs at the virtual ground of an inverting operational amplifier, signal swing is removed from the FETs to avoid distortion from signal-modulated ON resistance.

ON resistance error is achieved by compensating adjustment of the  $R_i$  resistors, but the thermal variation in  $r_{ON}$  continues to develop error.